Предложена методика изготовления транзисторов со сверхтонкими слоями составных полупроводников

Друзья, с момента основания проекта прошло уже 20 лет и мы рады сообщать вам, что сайт, наконец, переехали на новую платформу.

Какое-то время продолжим трудится на общее благо по адресу

На новой платформе мы уделили особое внимание удобству поиска материалов.

Особенно рекомендуем познакомиться с работой рубрикатора.

Спасибо, ждём вас на N-N-N.ru

Инженеры из США и Тайваня сконструировали качественные полевые транзисторы на основе составного полупроводника, арсенида индия InAs, размещённого на кремниевой подложке.

Предложенная методика позволяет получить высокую подвижность носителей заряда, характерную для полупроводников группы III-V, с применением малозатратной и прекрасно отработанной кремниевой технологии производства. Помимо арсенида индия, в группу III-V (цифры здесь обозначают положение компонентов полупроводника в периодической системе) входят, к примеру, нитрид алюминия, арсенид галлия и фосфид индия.

К сожалению, вырастить на кремнии слой составного полупроводника очень сложно, поскольку кристаллические структуры двух материалов сильно различаются. Авторы выбрали другой вариант схемы изготовления, в котором на подложку переносятся готовые образцы InAs.

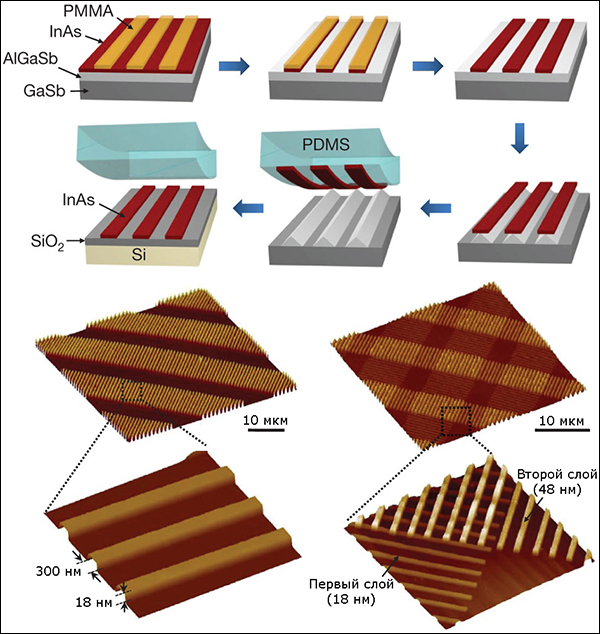

Рис. 1. Схема процесса изготовления транзисторов и изображения массивов нанолент InAs на Si/SiO2-подложке, помещённых под атомно-силовой микроскоп. Справа внизу показано размещение нанолент в два слоя толщиной в 18 и 48 нм. (Иллюстрация из журнала Nature).

Рис. 1. Схема процесса изготовления транзисторов и изображения массивов нанолент InAs на Si/SiO2-подложке, помещённых под атомно-силовой микроскоп. Справа внизу показано размещение нанолент в два слоя толщиной в 18 и 48 нм. (Иллюстрация из журнала Nature).

Опыты начинались с выращивания монокристаллических плёнок арсенида индия толщиной 10–100 нм на подложке из антимонида галлия GaSb, покрытой 60-нанометровым слоем Al0,2Ga0,8Sb. Затем на плёнку наносились полосы полиметилметакрилата (PMMA), и путём травления с использованием лимонной кислоты и перекиси водорода учёные формировали наноленты InAs. Для того чтобы перенести их на новое основание, слой Al0,2Ga0,8Sb выборочно вытравливался раствором гидроксида аммония.

В завершающей стадии процесса наноленты отрывались с помощью пластинки из полидиметилсилоксана (PDMS) и перемещались на совершенно стандартную Si/SiO2-подложку. После этого исследователи формировали никелевые электроды, завершая подготовку транзисторов к тестированию, которое они прошли вполне успешно.

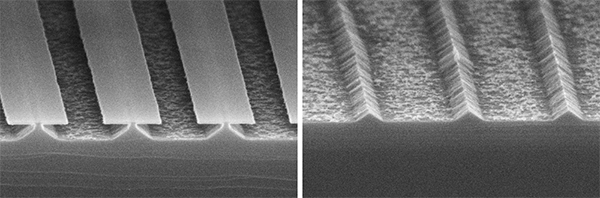

Рис. 2. После травления Al0,2Ga0,8Sb наноленты уносятся с исходной подложки. (Иллюстрация из журнала Nature).

Рис. 2. После травления Al0,2Ga0,8Sb наноленты уносятся с исходной подложки. (Иллюстрация из журнала Nature).

Авторы также изготовили несколько более сложные транзисторы с верхним затвором, изолирующий слой которого был выполнен уже не из SiO2, а из диоксида циркония. Эксперименты показали, что предварительное термическое окисление арсенида индия, формирующее нанометровый слой InAsOх, значительно улучшает свойства перехода между полупроводником и диэлектриком и повышает характеристики готовых устройств.

В будущем исследователи планируют провести эксперименты с другими составными полупроводниками и попробуют увеличить размеры используемых кремниевых подложек, постепенно подготавливая технологию к практической реализации.

Полученные результаты опубликованы в статье:

Hyunhyub Ko, Kuniharu Takei, Rehan Kapadia, Steven Chuang, Hui Fang, Paul W. Leu, Kartik Ganapathi, Elena Plis, Ha Sul Kim, Szu-Ying Chen, Morten Madsen, Alexandra C. Ford, Yu-Lun Chueh, Sanjay Krishna, Sayeef Salahuddin & Ali Javey

Ultrathin compound semiconductor on insulator layers for high-performance nanoscale transistors. – Nature 468, 286–289 (11 November 2010) doi:10.1038/nature09541.

По материалам:

- Источник(и):

- Войдите на сайт для отправки комментариев

Сайт о нанотехнологиях #1 в России

Сайт о нанотехнологиях #1 в России