Новая архитектура 3D-чипов позволяет устранить узкое место интерфейса процессор-память

Друзья, с момента основания проекта прошло уже 20 лет и мы рады сообщать вам, что сайт, наконец, переехали на новую платформу.

Какое-то время продолжим трудится на общее благо по адресу

На новой платформе мы уделили особое внимание удобству поиска материалов.

Особенно рекомендуем познакомиться с работой рубрикатора.

Спасибо, ждём вас на N-N-N.ru

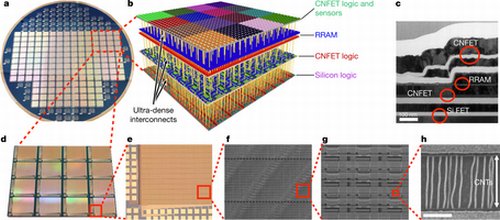

Будущим процессорам предстоит работа по обработке огромным массивов информации, количество которой растет буквально с каждым днем. Но производительность вычислительных систем, построенных на базе традиционной архитектуры, зависит не только от вычислительной мощности центрального процессора, одним из факторов, ограничивающих производительность системы, является недостаточная ширина полосы пропускания интерфейса между процессором и оперативной памятью. Решением этой проблемы может стать новая архитектура 3D-чипов, разработанная специалистами из Массачусетского технологического института и Стэнфордского университета. Опытный образец чипа с такой архитектурой состоит из несколько слоев, на которых расположены логические схемы и ячейки резистивной памяти, изготовленные из углеродных нанотрубок.

Опытный образец 3D-чипа является «самой сложной электронной схемой, изготовленной при помощи современных нанотехнологий». Использование углеродных нанотрубок позволяет избежать использования высокотемпературных производственных этапов, во время которых могут повредиться чувствительные элементы ячеек резистивной памяти.

Опытный образец чипа состоит из четырех слоев. Первым слоем является достаточно обычная кремниевая подложка на поверхности которой находятся достаточно обычные кремниевые логические цепи, выполняющие вспомогательные функции. Вторым слоем является собственно слой процессора, схема которого состоит из 2 миллионов транзисторов на базе углеродных нанотрубок. Третьим слоем является массив из одного миллиона ячеек резистивной памяти, а на последнем слое находятся дополнительные логические цепи и активные элементы датчиков, построенные на основе все тех же углеродных нанотрубок. Все слои связаны с другими при помощи металлических межслойных соединений.

Как уже упоминалось выше, на верхнем слое опытного образца 3D-чипа располагался слой чувствительных элементов на базе углеродных нанотрубок, количество которых в данном случае составляло один миллион. Для демонстрации работы этих датчиков процессор чипа был запрограммирован для работы в качестве химического анализатора, который после этого оказался способным различать находящиеся в воздухе химические соединения, т.е. различать запахи.

Но самым главным в новой архитектуре 3D-чипов является то, что процессор и массив оперативной памяти находятся в непосредственной близости друг от друга. Связывающие их металлические проводники имеют минимально возможную длину, что обеспечивает максимально возможную скорость обмена данными между памятью и процессором. И это, как несложно догадаться, служит решением проблемы узкого места, о которой упоминалось в самом начале.

И в заключение остается добавить, что данные работы проводились по заказу Управления перспективных исследовательских программ Пентагона DARPA и частично финансировались американским Научным фондом. На следующем этапе исследователи из Массачусетского технологического института и Стэнфордского университета будут работать совместно со специалистами известной компании Analog Devices, разрабатывая новые варианты реализации технологий 3D-чипов. К сожалению, как и в случае с массой других проектов, в которых используются углеродные нанотрубки и графен, невозможно и предположить, когда же именно эти технологии доберутся до уровня их практического применения.

- Источник(и):

- Войдите на сайт для отправки комментариев

Сайт о нанотехнологиях #1 в России

Сайт о нанотехнологиях #1 в России