Intel меняет наименования техпроцессов

Друзья, с момента основания проекта прошло уже 20 лет и мы рады сообщать вам, что сайт, наконец, переехали на новую платформу.

Какое-то время продолжим трудится на общее благо по адресу

На новой платформе мы уделили особое внимание удобству поиска материалов.

Особенно рекомендуем познакомиться с работой рубрикатора.

Спасибо, ждём вас на N-N-N.ru

Когда-то в стародавние времена усовершенствование процессоров Intel считалось на «раз-два» (или «тик-так» в терминологии компании): на счет «раз» уменьшался техпроцесс производства процессоров, на счет «два» — улучшалась микроархитектура в рамках неизменного техпроцесса. Затем ходики сломались, и 14-нм техпроцесс стал прирастать плюсами, символизирующими повышение производительности в рамках одной меры.

Текущий актуальный техпроцесс вообще называется 10nm SuperFin, но это ненадолго: на смену ему приходят новые индексы, и следующий будет называться Intel 7. Коротко, но не просто.

Исторически мера техпроцесса характеризовала длину затвора транзистора, однако по мере усложнения его структуры в таком виде она становилась все менее и менее показательной. Поэтому в Intel аналогично другим производителям приняли решение включить в состав новых индексов «виртуальный (или эквивалентный) размер элемента», не имеющий связи с каким-либо конкретной характеристикой процессора. Главной же величиной, обозначаемой индексом и характеризующей конкретное поколение, является прирост производительности по сравнению с предыдущим.

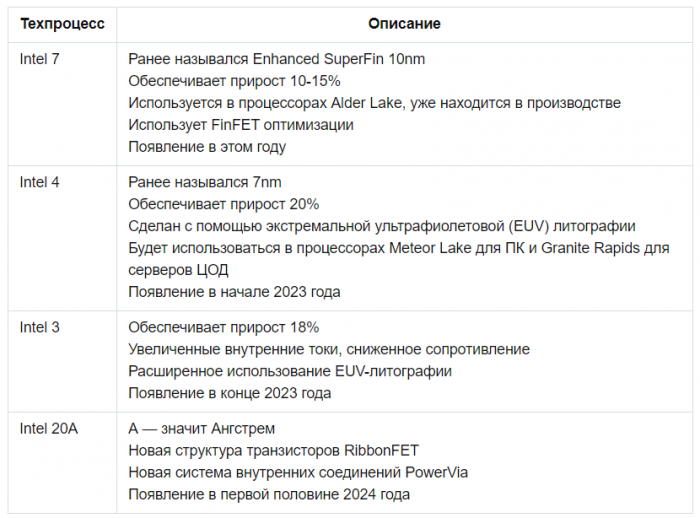

В период до 2025 года совершенствование техпроцессов Intel будет происходить по следующей схеме.

Некоторые пояснения по таблице. Прирост производительности указывается в пересчете на ватт мощности по сравнению с предыдущим поколением.

Транзисторы RibbonFET имеют принципиально новую внутреннюю структуру, называемую Gate All Around (GAA, каналы, полностью окружённые затворами). Такие транзисторы обеспечивают более высокую скорость переключения при меньшей занимаемой площади благодаря структуре с несколькими наноканалами.

Технология PowerVia предусматривает разведение сигнальных шин и цепей питания по разные стороны силиконовой подложки. Это позволит существенным образом улучшить отношение сигнал/шум в каналах передачи данных и дополнительно повысить эффективную плотность размещения транзисторов на кристалле.

- Источник(и):

- Войдите на сайт для отправки комментариев

Сайт о нанотехнологиях #1 в России

Сайт о нанотехнологиях #1 в России